CSCI 1120 Lecture Notes - Lecture 7: Memory Buffer Register, Von Neumann Architecture, Memory Address Register

CSCI 1120 verified notes

7/39View all

Document Summary

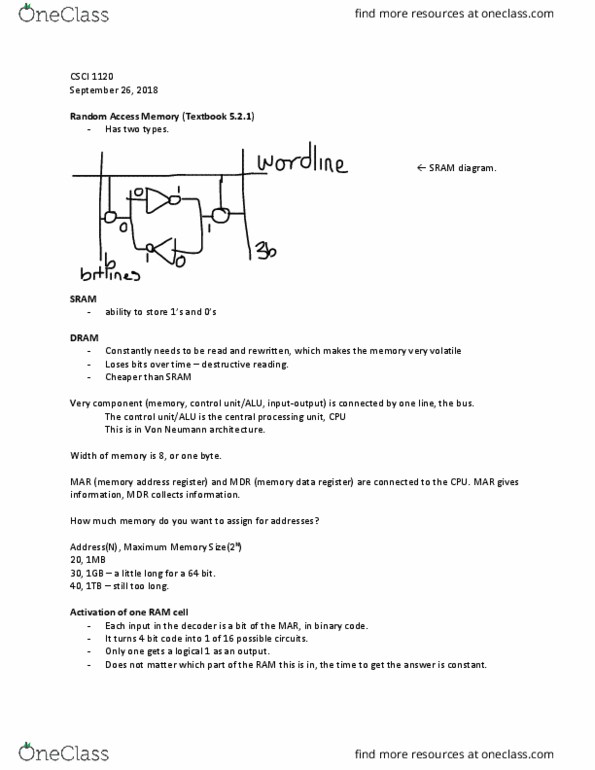

Constantly needs to be read and rewritten, which makes the memory very volatile. The control unit/alu is the central processing unit, cpu. Very component (memory, control unit/alu, input-output) is connected by one line, the bus. Width of memory is 8, or one byte. Mar (memory address register) and mdr (memory data register) are connected to the cpu. 30, 1gb a little long for a 64 bit. Each input in the decoder is a bit of the mar, in binary code. It turns 4 bit code into 1 of 16 possible circuits. Only one gets a logical 1 as an output. Does not matter which part of the ram this is in, the time to get the answer is constant. Technically, it is difficult to produce something like this, in one line. So the solution is to split it into two chunks, both of 210.